本文提出了一种基于低成本FPGA的高清低码流安防摄像机SoC实现方式,该设计已经完全实现,开创了高清低码流安防摄像机SoC的先河。

概述

目前高清H.264摄像机的核心SoC基本上都是ASIC,而FPGA作为近年来发展迅速的可编程器件,在高清H.264摄像机的SoC领域如何能有一席之地?这是我们的设计需要实现的目标。

设计特点

与ASIC相比,FPGA的特点是功能强,设计灵活,随时升级,工作成果可以积累,NRE低,但是芯片价格比ASIC贵,所以必须找到一个可以达到价格平衡的应用领域,我们根据这几年智能手机和3G网络发展迅猛的情况,参考电信运营商第一代全球眼的技术指标,直接把设计指标定位在码流小于 512kbps和分辨率为1280x720x25fps,目前在市面上可以实现这些指标的摄像机几乎没有,这是FPGA的好机会。

512kbps的码流限制主要是考虑到ADSL和家庭光端机的上传能力,而且也能利用3G上传视频,减少了智能手机的码流下载压力;1280x720是智能手机的主流分辨率,自然需要相应的视频源,如果显示D1或CIF,效果肯定不理想。

我们的目标是做一个可以直接用于生产的参考设计,除了设计指标先进,我们还要考虑价格和实用,所以我们选择了低成本的CYCLONE IV系列,另外也实现了一般网络摄像机的全部功能,如H.264压缩、720p25帧三码流、双向语音、重要区域和隐私区域的定义、智能分析、移动检测、 声音侦测、POE供电等。

实现高清低码流H.264摄像机SoC的关键

一般来说,1280×720×25fps的码流在2Mbps左右,如何降低码流?除了使用mail profile with cabac的H.264编码器外,还需要对视频图像进行分析,而且要在帧率、分辨率、视频质量等方面权衡折中,在512kbps码流下获得最好的视频效果,为了达到这样的目的,需要复杂灵活的控制,FPGA可以满足这样的需求。

高清低码流H.264摄像机的结构

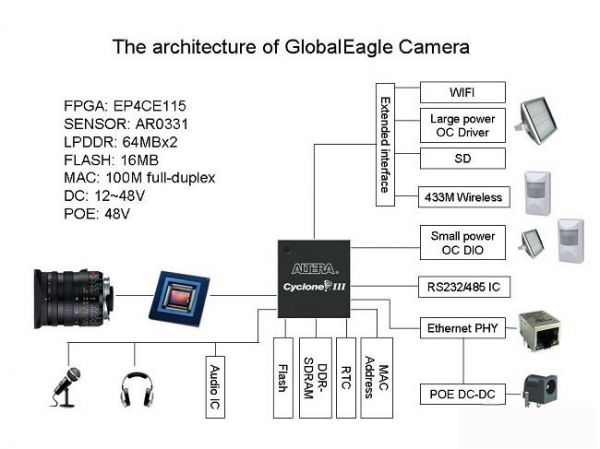

高清低码流H.264摄像机的结构简图如下:

FPGA的选用

在高清低码流H.264摄像机的结构中,除了图像传感器、存储器、电源和模拟接口外,所有的功能如图像处理、H.264编码、协议处理、参数管理、媒体流发送等都由FPGA实现,FPGA就是高清低码流H.264摄像机的 SoC;目前世界上FPGA的生产商只有几个,可选择的产品也不多,要用FPGA实现高清低码流H.264摄像机的SoC,选择一款合适的FPGA非常重要,FPGA的选择主要考虑三方面的因素:速度、成本和结构;每个FPGA生产商都有多个FPGA系列,每个系列的速度、性能和价格都不同,要使高清低码流H.264摄像机SoC的成本尽可能低,应该选择成本最低的系列,像我们选择的FPGA是Altera公司的CYCLONE IV系列,型号是EP4CE115F23C8,CYCLONE IV是低成本系列,在同样是低成本系列的FPGA中,CYCLONE IV的速度是最快的; FPGA的结构对图像处理也很重要,尤其是存储器和乘法器的数量,H.264算法是以宏块为单位,在处理过程中必然会涉及到宏块的输入输出和缓存,1个宏 块的数据为384字节(256字节亮度数据和128字节色度数据),如果考虑到输入输出和处理的并行,必须设置双份,即768字节,用CYCLONE IV的1个M9K存储块正好,从上面的分析可以看出适合图像处理的FPGA对内部存储器的要求是存储块容量小(如1KB)、存储块数量多,另外,对乘法器的要求也是数量多;在我们选择FPGA的时候,CYCLONE IV是在所有低成本FPGA中有最大的存储器逻辑比和乘法器逻辑比,很适合做图像处理。

图像传感器的选择

为 了满足1280x720x25fps的要求,只需要选择百万像素的传感器就可以了,我们最终选择了300万像素的AR0331,还可以实现 1920x1088x11fps,在实现1280x720x25fps时还有电子PTZ功能,AR0331还有宽动态功能,便于摄像机以后扩充宽动态功能。