网上有很多关于fpga的总结和分析,但都是基于软件调试的角度来进行分析的,本文则选择了FPGA硬件的电路板来进行相关的分析,并且着重FPGA电路板的可测试性设计。所谓可测试性,很简单,就是在板级调试的时候,更方便调试,判决准则就是想看什么信号就可以看到什么信号。

电源电路设计

在进行电源电路的设计时,我们可以在电路的输出处增加一些跳线,在电源电路没有调通之前,可以确保电源不会输出到下一部分电路,保证后续电路的安全,而电源电路部分,应该加上足够的测试点,包括反馈电压点、输出电源点以及地测试点,建议在PCB设计的时候,在电源输出测试点处就近放一个地测试点,个人不建议测量电压的时候,万用表的表笔直接点在电容或者电感上。

建议用LED指示灯来标记电源的输出处,这样的话板子是否进行正常的工作就一目了然了。

FPGA信号测试

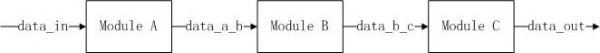

曾经做过FPGA半调试的朋友肯定都有这样的感觉,当板子的调试出现问题时,非常想把板子拆开,然后把逻辑分析仪或者数字示波器接入到内部信号通道的每个模块的输入输出端口处,看下波形,分析问题到底出在什么地方。虽然有chipscope/signaltap这样的辅助分析工具,但FPGA内部资源毕竟有限,不可能做到随意查看信号。

所以我们可以从FPGA上入手,如果在设计上还有未使用的引脚,我们可以引出8根或者16根线来,作为专用调试管脚,在PCB设计时连到一个排插上,用于调试,观察内部节点信号的波形,以下图为例,进行描述: