随着多媒体技术的迅速发展以及3G时代的到来,人们对多媒体的要求越来越高,各种组织提出了多种视频算法。国际标准化组织制定了许多国际标准来规范多媒体技术的发展。在多媒体通信终端设备方面,TI公司的开放式多媒体应用平台OMAP(Open Multimedia Application Platform)体系结构,综合了ARM处理器的控制能力与DSP的运算能力,可以实现单一DSP无法完成的更多、更复杂的服务(如实时视频交互)等。TI公司1998年就推出了可扩展的开放式0MAP处理器平台,先后推出了0MAP310、0MAP710、OMAPl510、0MAPl610、OMAP2410与OMAP2420等处理器。2008年推出的OMAP3架构的器件(0MAP3503、OMAP3515、OMAP3525以及OMAP3530),由ARM Cortex-A8内核和DSP TMS320C64X+内核组成,具有更强大的控制功能和运算功能。由于OMAP系列处理器一直强调向上兼容性,所以系列之间的通用性很强,结构变化不大,程序便于移植。

本文以OMAP3530为例,分析了0MAP平台的硬件结构与软件编程特点;总结了TI公司提供的专用图像图形处理库(IMGLIB)的使用技巧,并与OMAPl510进行了部分比较;在流行的视频编解码标准的基础上,提出了基于OMAP3的视频解码器的通用解码方案。

1 OMAP平台简介

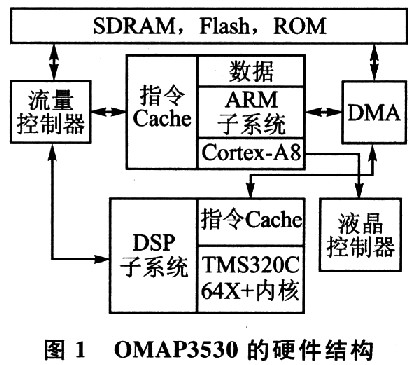

开放式多媒体应用平台OMAP结合高性能、低功耗的DSP核与控制性能强大的ARM内核,是一种开放式的、可编程的体系结构,目前主要有OMAP1X、OMAP2X和OMAP3X系列。以OMAP3530为例,硬件结构如图1所示。

0MAP3530的硬件平台主要由ARM内核、DSP内核以及流量控制器(Traffic Controler,TC)组成。

(1)ARM内核

OMAP3530采用ARM Cortex-A8核,工作主频最高可达720 MHz。它包括存储器管理单元、16 KB的高速指令缓冲存储器、16 KB的数据高速缓冲存储器和256K字的二级Cache;片内有64 KB的内部SRAM,为液晶显示等应用提供了大量的数据和代码存储空间。CortexA8内核采用13级流水线、32位的RISC处理器架构。系统中的控制寄存器对MMU、Cache和读写缓存控制器进行存取操作。ARM内核具有整个系统的控制权,可以设置DSP、TC以及各种外设的时钟及其他工作参数,控制DSP的运行停止。OMAP3530平台可支持包含绘图、多媒体内容和Java程序的先进应用。