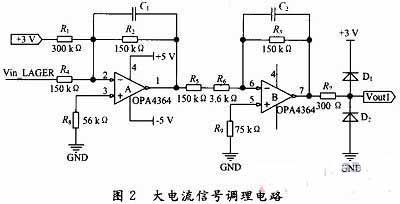

图2为每一相大电流信号滤波、平移、放大和限幅电路。由于A/D转换器输入电压范围为0~3 V;而输入信号是直流偏移电平为0 V的交变正弦波,所以设计电平偏移电路抬高电流信号。低通滤波和信号放大由两级运放组成。

2.2 脱扣电路模块设计

脱扣电路分为数字脱扣与模拟脱扣数字脱扣电路较为简单,DSP通过I/O口输出脱扣信号,经过光耦隔离放大驱动磁通线圈。模拟脱扣电路采用比较器电平鉴幅电路实现,每一相电流采用两个比较器来完成,当微处理器没有发出脱扣信号且电流信号的幅值在参考基准电压范围内,则比较器并联输出一高电平,否则为低电平。低电平信号通过脉宽检测电路,进行抗干扰处理。如果低脉冲维持一定的宽度则单稳态触发器被触发,同时输出一定宽度的脉冲通过驱动电路使磁通变换器打开,从而分断断路器。模拟脱扣电路如图3所示。

比较器电平鉴幅电路在实际应用中,由于干扰的存在,比较器的输出会出现一些不必要的窄脉冲,因此设计了脉宽检测电路用于滤除干扰尖峰引起误触发脱扣动作。在设计时,当输入脉冲宽度大于1ms时,输出32.9ms的脱扣信号;当小于1ms时,不输出脱扣信号。