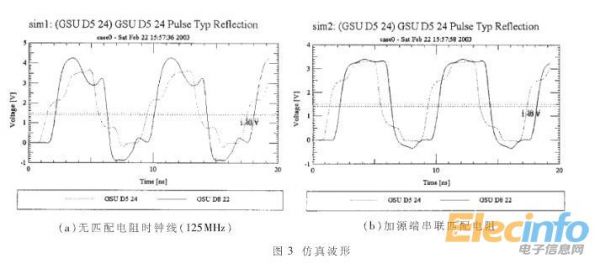

在实际仿真中首先就时钟和数据的信号完整性进行分析仿真,通过适当的端接匹配得到较好的接收波形。图3是一组无源端匹配和有源端匹配时钟线的不同仿真波形比较,从中可以看出首先进行信号完整性仿真的必要性。

在公共时钟同步时,数据发送和接收必须在一个时钟周期内完成。同时,器件延时和PCB走线延迟也限制了公共时钟总线的理论频率,所以公共时钟同步普遍用于低于200MHz~300MHz的传输速率,高于这个数值的就应引入源同步技术。源同步技术工作在相对时钟系统下,采用数据和时钟并行传输,传输速率主要由数据和时钟信号间的时差所决定,这样可使系统达到较高的传输速率。

本文通过对宽带以太网交换机主机和子卡板进行信号完整性分析、时序分析及仿真,明显缩短产品设计周期,通过仿真解决高速设计中出现的信号完整性、时序等方面问题,充分保证整个系统的质量和设计速度,真正做到PCB板一次通过的性能保障。