2.3 继电器电阻驱动电路模块:

继电器电阻驱动电路模块主要是FPGA根据键盘输入的电阻值,判断相应的一些电阻是否要接入,从而使电阻对应的继电器闭合或断开,给予其对应的信号1或0即可。

2.4 仿真结果:

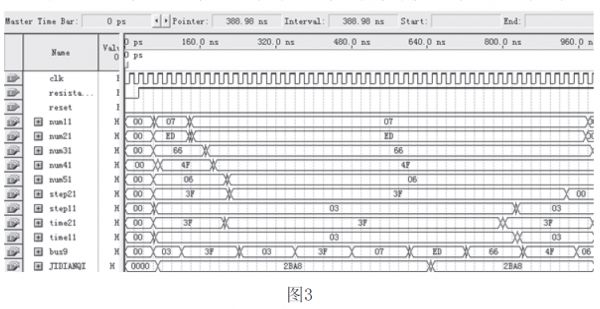

由上述理论可知,电阻1的产生原理和电阻2的产生原理完全一样,为了使仿真结果更加明了,这里的仿真波形只用电阻1来验证其正确性,其仿真波形如图3所示。

此图是仿真图中的一部分,只选择了几个有代表性的信号显示出来加以说明,从图中可以看出有时钟信号clk,复位信号reset,电阻1选择信号resistance1,num11至num51显示的分别是电阻值的小数位、个位、十位、百位、千位。step11和step21分别显示的是当前工作的步数的个位和十位,其中time11和time21分别显示的是工作时间的个位和十位。Bus9则是动态显示时的数据信号,JIDIANQI则代表的是16个继电器的开关状态。从上图中可以看出该电阻的小数位的段码为07H,对应的二进制就是00000111,其对应显示的数字是7即小数位为7,同理可知其个位数为5,十位数为4,百位数为3,千位数为1,所以其阻值就为1345.7Ω,从图中可以看出总线上是循环传递着时间、步数和数值信息,根据阻值,其相应的继电器会闭合,根据上述电阻网络原理,J4、J6、J8、J9、J10、J12、J14闭合,其余的继电器均断开,即对应的二进制代码为(0010101110101000)B,换算成十六进制即为2BA8,从上图可以看出其验证结果是正确的。

3 结束语

系统通过引进FPGA来实现电阻提供这一模块,且将周围其他数字逻辑电路也集成至该芯片中。这样既解决了系统的特殊性,又增强了系统的抗干扰性,提高了控制精度,也简化了调试。此外,本系统还将驱动电路、编解码电路等硬件通过VHDL语言在FPGA芯片中实现,相比以前的模拟电路和单片机的实现方法,使用的元器件更少,体积也更小,针对不同场合,修改起来也更加方便。具有很好的市场前景。