3 系统功能单元实现

3.1 波形数据产生单元

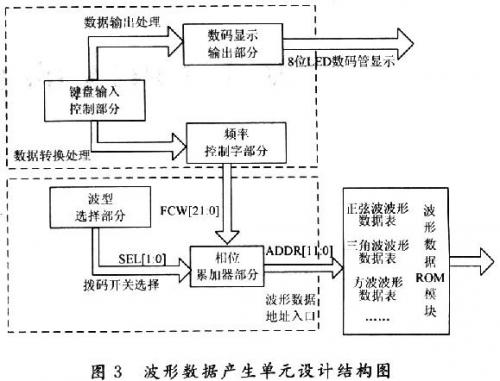

波形数据产生单元是信号发生器设计的主体。在此,采用DDS原理设计的信号发生器能完成三种波形(正弦、三角和方波)数据的产生,而且根据控制信号还可 完成选定波形指定频率的输出。波形数据产生单元按功能实现上的相互联系可划分为频率控制字生成模块、相位累加器模块和波形数据ROM表模块,如图3所示。 其中,频率控制字生成模块可根据输入产生指定频率字,同时显示输入频率数字。相位累加器模块负责对所选波形的相位寻址,以频率控制字作为步长反复进行累加运算。波形数据ROM表模块存放三种波形的幅值/相位量化值,通过地址选择相应波形的数据。

系统输入控制使用4×4键盘.键盘主要按键功能介绍如下:

“0~9”:数字键,设定信号频率;

“确定”:用于对波形信号设置的确认,波形信号的设置必须“确定”后才有效;

“←”:删除已输入信号频率数字的最后一位,用于修改设置的频率;

“清零”:将频率数字快速全部清零;

“↑”:步进增大控制;

“↓”:步进减小控制。

设定频率输出范围为1 kHz~10 MHz,频率步进为50 Hz。系统输出采用8个LED数码管,以扫描方式显示(单位为Hz)频率数字。根据DDS原理,以步进值50Hz作为频率控制字1,那么最大值10 MHz对应的频率控制字为200 000,用18位二进制数值就可以表示(218>200 000)。从抽样值恢复出原波形数据,理论上每个周期波形数据至少抽取2个点,考虑到实际应用时受频率损耗、线间串扰等因素的限制,该设计采用22 b的频率控制字和相位累加器,4 Kb的8位波形ROM表,取相位累加器输出的高12 b寻址波形数据,三种波形按幅值/相位对应关系分别存储782个数据。故各波形数据单位周期有800 768(782×210)个相位状态,完全满足任一波形在单位周期内取4个幅值点的要求,可保证即使输出最大频率的波形仍能达到较好的效果。波形选择功能由两位开关组合实现,共有四种状态,其中三组用来表征不同的波型,另一组留作扩展波形用。

3.2 D/A转换单元

数/模转换单元是继波形数据产生单元之后,将数字量形式的波形幅值转换成所要求的合成频率的模拟量形式信号。DAC输出信号实际上是阶梯模拟信号,需在数/ 模转换后利用低通滤波器对波形进行平滑处理。在此,采用ADI公司生产的单片双8位CMOS乘法数/模转换器AD7528,线性度达到1/2,转换时间达到纳秒级,可以很准确地进行10 MHz信号的量化运算。

3.3 滤波处理单元

滤波器是一种能通过有用频率信号而同 时抑制(或衰减)无用频率信号的电子装置。由于运算放大器具有近似理想的特性,且可以省去电感,得到接近理论预测的频率响应特性。构成有源滤波电路后还具有一定的电压放大和缓冲作用,并能减小体积。综合考虑,系统采用运算放大器SL560构成二阶低通滤波器。