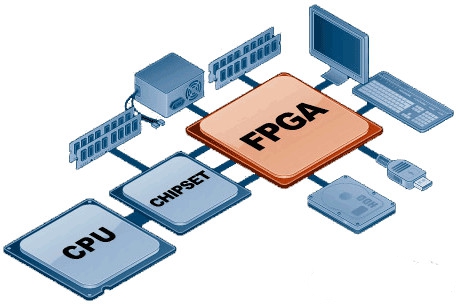

总归一句话,FPGA之所以可编程是因为可以通过特殊的01代码制作成一张张“真值表”,并将这些“真值表”组合起来以实现大规模的逻辑功能。不了解FPGA内部结构,就不能明白最终代码如何变到FPGA里面去的。也就无法深入的了解如何能够充分运用FPGA。现在的FPGA,不单单是有前面讲的那三块,还有很多专用的硬件功能单元,如何利用好这些单元实现复杂的逻辑电路设计,是从菜鸟迈向高手的路上必须要克服的障碍。而这一切,还是必须先从了解 FPGA内部逻辑及其工作原理做起。

2、错误理解HDL语言,怎么看都看不出硬件结构。

HDL语言的英语全称是:Hardware Description Language,注意这个单词Description,而不是Design。老外为什么要用Description这个词而不是Design呢?因为 HDL确实不是用用来设计硬件的,而仅仅是用来描述硬件的。

使用HDL的好处在于我们已经设计好了一个寄存器传输级的电路,那么用HDL描述以后转化为文本的形式,剩下的向更低层次的转换就可以让EDA工具去做了,这就大大的降低了工作量。这就是可综合的概念,也就是说在对这一抽象层次上硬件单元进行描述可以被EDA工具理解并转化为底层的门级电路或其他结构的电路。在FPGA设计中,就是在将这以抽象层级的意见描述成HDL语言,就可以通过FPGA开发软件转化为问题1中所述的FPGA内部逻辑功能实现形式。HDL也可以描述更高的抽象层级如算法级或者是体系结构级,但目前受限于EDA软件的发展,EDA软件还无法理解这么高的抽象层次,所以HDL描述这样抽象层级是无法被转化为较低的抽象层级的,这也就是所谓的不可综合。所以在阅读或编写 HDL语言,尤其是可综合的HDL,不应该看到的是语言本身,而是要看到语言背后所对应的硬件电路结构。

如果看到的HDL始终是一条条的代码,那么这种人永远摆脱不了菜鸟的宿命。假如哪一天看到的代码不再是一行行的代码而是一块一块的硬件模块,那么恭喜脱离了菜鸟的级别,进入不那么菜的鸟级别。