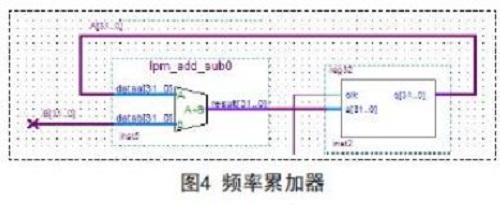

(3)频率累加器

频率累加器模块如图4所示,通过一个32位加法器跟32位寄存器构成频率累加器,频率控制字高4位为0.

(4)相位寄存器

相位寄存器模块如图5所示,通过一个8位加法器跟8位寄存器构成相位寄存器并产生8位波形数据地址。

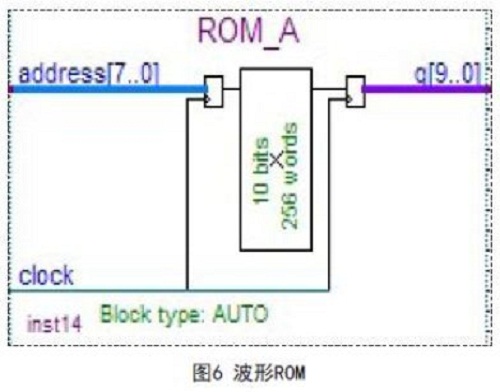

(5)波形存储器设计

波形数据ROM就是存放波形数据的存储器,大多波形发生器产品都将波形数据存放在外部的ROM中,这样使得各部分结构清晰,测试、维护更加方便但由于ROM本身读取速度慢的缺点,使得整个系统性能下降,工作频率下降,为了解决以上问题,本设计使用的是用FPGA设计出ROM,在FPGA中存放波形数据,使用Quartus II9.0中的Mega Wizard Plug-In Manager来生成一个ROM,如图6所示。