2 帧同步系统的VHDL设计与仿真

2.1 总体结构设计

根据实例需求,帧同步码组长度(LenCode)、帧同步码组(FrameCode)、容错位数 (ErrorNum)、帧长(Len-Frame)、校核态校核帧数(CheckNum)以及同步态校核帧数(SyncNum)均以常量的形式设置,便于 VHDL程序中修改同步参数。系统数据速率及时钟频率为50 MHz.

根据图2所示的结构,很容易想到采用状态机的设计方法来实现同步系统。不论是采用状态机方式,或原理图方式进行VHDL程序设计,最终均可以转换成VHDL代码的形式。显然,直接采用编写VHDL代码的形式,更利于程序的修改及升级维护。因此,本文完 全采用代码编写方式来进行程序设计。

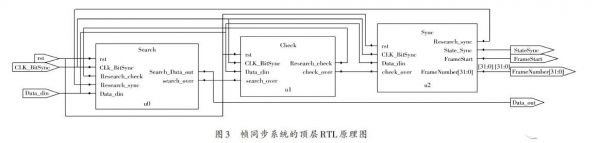

图2是一个典型的状态转移图,可以将转移条件看作状态之间的信号接口。 整个帧同步系统可以划分为搜索状态模块(Search)、校核状态模块(Check)及同步状态模块(Sync)。除了上电后启动搜索状态之外,当校核未 通过(CheckNum 帧内有一个校核帧未同步)或同步态失锁(连续SyncNum 帧未同步)时也需启动搜索状态,因此搜索状态的启动信号有复位信号(rst)、校核态重搜索信号(Research_check)和同步态重搜索信号 (Research_sync);校核态的启动信号仅来自于搜索态(search_over),即只有当搜索到帧同步码后才能转入校核态,如果校核通过则 送出校核完成信号(check_over),校核未通过则送出重新搜索信号(Research_check);同步态的启动信号仅来自于校核态 (check_over),只有校核通过后才能进入同步状态。进入同步态后,持续对同步码组进行检测,当检测到重新失锁后送出 Research_sync,重新启动搜索状态。图3为帧同步系统顶层VHDL程序文件采用Synplify Pro综合后的RTL原理图。

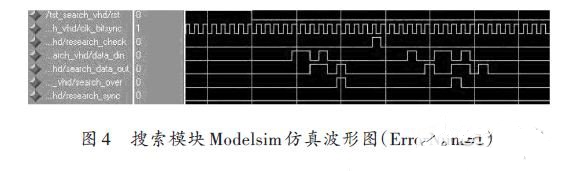

2.2 搜索模块的VHDL设计与仿真

搜索模块的对外接口如图3所示。其中,CLK_BitSync及Data_in分别为位同步时钟信 号和输入数据;Data_out为经2个时钟周期延时后的比特流数据。对输入数据的延时处理,是为了补偿产生search_over 时的处理时延,以便于脉冲信号search_over 与最后一位帧同步码对齐。

搜索输入比特流中的帧同步码组,首先需要将输入数据送入移位寄存器(Regdin)中,而后将 Regdin中的数据与帧同步码组相比即可。程序中将多路启动信号(rst、Research_check、Research_sync)取或后,作为异 步复位信号,用于启动一次搜索过程。搜索过程中,采用for循环对寄存器Regdin 与同步码组进行比较,通过逐位比较,每发现1 b不相同,则计数加1,计算出两者之间的汉明距离。计算完汉明距离后,判断是否大于容错门限ErrorNum,如大于容错门限则继续搜索,否则输出同步脉 冲search_over,并停止搜索。

图4为搜索模块的Modelsim仿真波形。其中,帧同步码长度LenCode=7, 帧同步码FrameCode=“1011000”,容错门限ErrorNum=1.可以看出,复位后首先搜索到一次帧同步码组;当 Research_check为高电平,启动另一次搜索过程,比特流中搜索到“1001000(ErrorNum=1)”时,此时容错位数设置为1,因此 输出同脉冲search_over,并停止搜索过程,即使后续比特流中出现了“1011001(ErrorNum=1)”,仍然不输出同步脉冲。

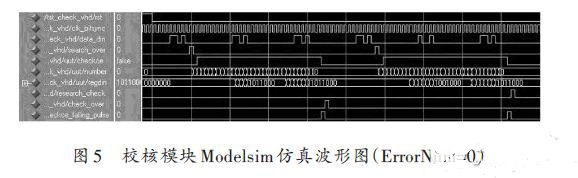

2.3 校核模块的VHDL设计与仿真

为便于程序编写,校核模块主要由Check_Ce 进程和Checking 进程组成。Check_Ce 进程用于检测search_over信号,检测到信号出现高电平后,产生长度为CheckNum 帧数据的高电平允许信号CheckCe,并通过计数器Number 来标识每帧中数据及同步码组的位置。产生了CheckCe及Number信号后,Checking进程只需在CheckCe信号为高电平的范围内对同步码 组进行校核即可。校核完成后,需要使check_over(连续CheckNum帧均同步)或research_check(CheckNum帧内有一帧 未同步)信号产生一个高电平脉冲。帧校核的方法与搜索同步码组的方法类似,即通过汉明距离来判断是否同步。将校核态分成Check_Ce进程和 Checking进程来分别进行实现,则每个进程的功能划分更为简单,编程实现时也相对容易得多。

图5 是校核模块的Modelsim 仿真波形。其中,帧长度LenFrame=16,校核帧数CheckNum=2,容错门限ErrorNum=0,其余参数与搜索模块相同。从波形上很容易 看出,当search_over第一次出现高电平时,其后连续两组同步码均为“1011000(ErrorNum=0)”;当search_over第二 次出现高电平时,其后第一组同步码为“1001000(ErrorNum=1)”,第二组同步码为“1011000(ErrorNum=0)”。因此第一 次帧校核顺利通过,校核完成后check_over输出一个高电平脉冲,research_check保持为低电平;第二次校核未通过,校核完成后 research_check输出一个高电平脉冲,check_over保持为低电平。