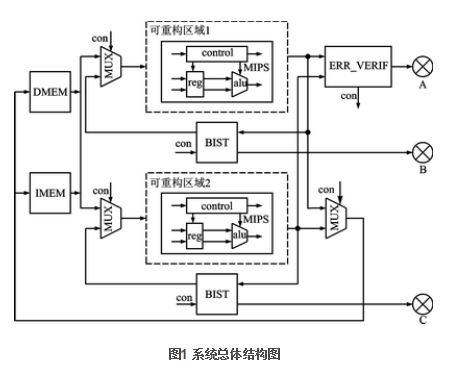

在图1中,以虚线框起来的部分为FPGA中的可重构区域。图中有两个可重构区域,上一个区域为主子系统区,下面一个区域为主子系统区的备份区。

2 工作原理

系统上电复位后,在两MIPS内部逻辑均正常的情况下,系统执行过程为:指令存储器根据系统复位后的指令执行地址将指令从IMEM中取出,送入两个MIPS系统中;两个MIPS处理器分别在指令的指示下完成相应的工作,然后将执行结果输出到ERR_VERIF模块、DMEM和IMEM模块;ERR_VERIF模块分析系统是否正常运转,然后将分析结果信息输出到FPGA上的LED灯A上。

当其中一个MIPS处理器的内部逻辑发生故障时,可假定为图1中上方的主MIPS区域故障。系统执行过程为:ERR_VERIF故障检测模块检测到系统的子区域出现故障,然后发出故障位置检测控制信号;此时,BIST模块接收到检测控制信息后,启动内建自测试系统,将故障测试向量输入MIPS系统。在开启了BIST模块后,系统的指令输入将不再来自IMEM模块,而是由BIST模块提供。同时,指令的执行结果也不会写回到DMEM模块中,而是反馈到BIST模块中。MIPS根据测试向量进行运算,然后将运算结果反馈给BIST单元。BIST单元的测试要进行多次,以确保对故障的准确判断。BIST得到执行结果后,对测试结果进行分析并判定当前MIPS系统是否正常运行,最后分别将分析结果输出到FPGA上的LED灯B、C上。

ERR_VERIF模块的故障分析方法为比较法。它将执行同样指令且同步运行的两个子系统的执行结果进行比较,当发现结果不一致时,就表示其中一个子系统出现了故障,这时需要使用BIST模块去主动定位故障位置。而BIST进行故障分析的方法与ERR_VERIF模块使用的方法本质上是相同的,但是实现方式不同。BIST模块将被测试模块产生的输出与BIST内部存储好的预期的输出进行比较,来测试被测模块是否出现故障。

检测出的故障情况有3种:主子系统故障、备份子系统工作正常;主子系统正常、备份子系统故障;主系统子系统和备份子系统均出错。BIST模块检测出故障情况后,会将故障情况显示于故障灯(也就是A、B、C)上。当3个故障灯中有灯亮时,则表示系统出现故障。灯A、B亮,表示主子系统出现故障;灯A、C亮,表示备份子系统出现故障;灯A、B、C亮,表示两子系统均出现了故障。在出现故障后,系统会根据具体情况,对系统输出进行调整。当主子系统出现故障而备份子系统未出现故障时,系统输出则来自备份子系统;当备份子系统出现故障而主子系统未出现故障,系统输出则来自主子系统。当两子系统都出现了问题时,则需要停机维护。当其中一个子系统出现故障时,需要将无故障的子系统比特流重新下载入FPGA系统中。在下载时,系统的工作无需停止。

3 内建自测试技术与BIST结构分析

内建自测试技术(Buildin Self Test,BIST)是指在设计电路时,为了及时监测系统的状态,而设计一部分自测试电路来测试电路运行是否正常。BIST系统主要组成部分有测试向量生成、测试输入隔离、输出结果反馈分析和测试控制等,如图2(a)所示。