ESL 的目标受众

ESL 流程对预期 FPGA 用户的主要好处是其生产率和易用性。通过将产生硬件电路的实现细节进行抽象,这些工具向以软件为中心的用户群(图 1)发出了召唤。在更高的抽象级别上工作,使拥有 C 语言等传统软件编程语言技能的设计者能够更快地以硬件探究其想法。以软件为中心的应用程序和算法开发者已将该方法的优点应用于 FPGA,他们包括系统工程师、科学家、数学家、和嵌入式与固件开发者。适合 ESL 方法学的应用程序的特征包括具有大量内循环的计算密集型算法。这些应用程序可以通过硬件中的并发并行执行实现巨大加速。ESL 工具已在音频/视频/图像处理、加密、信号与分组处理、基因排列、生物信息、地球物理和天体物理等应用领域成功帮助进行了项目部署。

ESL 设计流程

与 FPGA 相关的 ESL 工具包含两个主要设计流程。

1. 高级语言 (HLL) 综合。HLL 综合覆盖算法或行为综合,可从C或C类的软件语言生成硬件电路。各种合作伙伴解决方案采用不同的方法将高级设计描述转换为 FPGA 实现。如何完成这一点构成了各种 ESL 产品之间的根本不同。

您可以将 HLL 综合用于各种应用情况,包括:

模块生成。在这种使用模式下,HLL 编译器可以将以 C 表示的功能块(例如一个 C 子程序)转换成相应的硬件块。生成的硬件块随后被收入整个硬件/软件设计,这样HLL 编译器生成了整个设计的一个子模块。模块生成通过快速生成,然后集成算法硬件组件,允许软件工程师参与整个系统的设计。那些寻求以更快的方式构建新的、以计算为导向的硬件块的硬件工程师们,也可以使用模块生成。

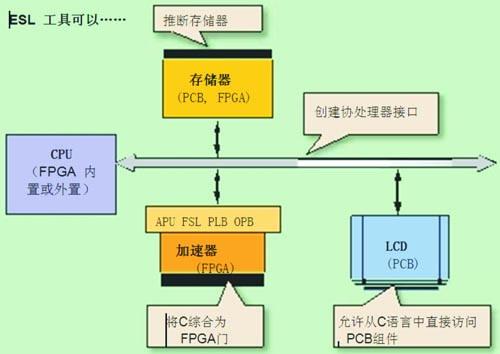

处理器加速。在这种使用模式下,HLL 编译器允许通过在 FPGA 的可编程结构中创建定制加速器块,来加速在处理器中运行的时间关键功能或瓶颈功能。除创建加速器外,这些工具还可以自动推断存储器并生成所需的硬件-软件接口电路,以及实现处理器与硬件加速器块之间通信的软件设备驱动程序(图 2)。与运行在 CPU 中的代码相比,FPGA 加速的代码其运行速度可以快几个数量级,而消耗的功率则大大降低。