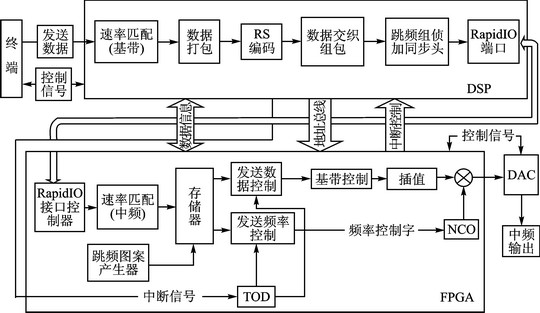

图3 跳频发射机结构框图

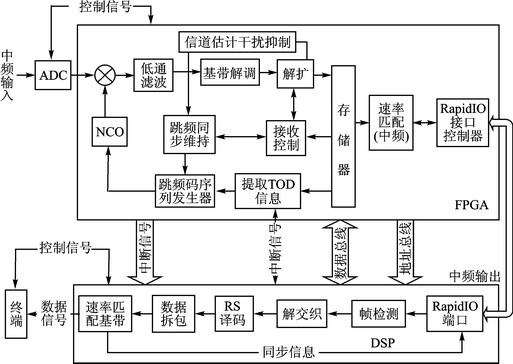

图4 跳频接收机结构框图

当接收信号到达接收端后,经过前端电路的模拟中频信号将通过宽带A/D 转换器转化为数字信号,并送入FPGA 经行中频处理(频谱下搬移过程),FPGA在把解调以后的数字基带信号送入DSP,DSP 在完成接收基带处理以后,将把信息序列送入远端的语音终端或数据终端,这样就完成了一次完整的通信过程。

对于其中的处理器,本课题选用了TI公司的DSP 芯片TMS320C6487TCI和Xilinx公司的FPGA VIRTEX5 XC5VSX50T668作为高速跳频系统实现的硬件架构载体。其中Xilinx公司的Virtex5系列采用第二代 ASMBL(高级硅片组合模块)列式架构,包含5种截然不同的平台(子系列),比此前任何 FPGA系列提供的选择范围都大,它具有运算速度高、使用灵活、功耗低等优点,可以快速地完成数字信号处理中的特殊运算。

2 系统设计

跳频发射机系统包括基带处理部分和中频处理部分,基带处理部分由FPGA和DSP完成,主要处理包括:产生发送消息,进行信道编码[5]、交织,按帧格式进行打包,写入FPGA内部消息存储器,生成跳频图案、跳频数、跳时等参数,写入FPGA内部频率表存储器、跳频数寄存器和跳时寄存器。中频处理部分由FPGA和AD/DA完成,主要处理包括:存储器控制、基带调制、脉冲成形、数字上变频,发送数据控制和跳频控制。为了提高数据的传输速率,处理器之间使用DSP芯片的RapidIO端口进行数据交换,基带板和中频板通过高速SERDES方式转换数据进行传输。