(3) 数据跳帧结构

数据跳帧格式如下:

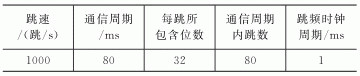

由于以9.6 kbps的用户速率传送96字节数据需要80 ms时间,经过Rs编码与交织等处理后,整包数据变为152字节。传送152字节数据,使用1000跳/s的跳速,76个数据跳全部发送完毕。剩余的4 ms时间内插入4个频点的勤务同步跳,共4跳,作为勤务同步和迟入网同步。因此本跳频系统中设计了一个跳频通信周期为80 ms,如表1所列。

表1 各时钟关系

一个通信周期为80 ms,每1 ms容纳32个基带位(基带速率为32 kbps)。

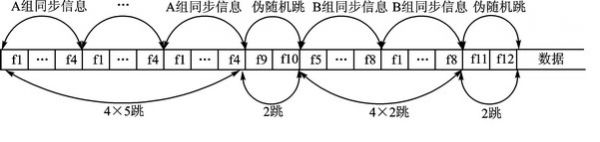

发端在按下PTT(Push To Talk)键时先发送一组同步头,用来传送初始同步信息[10],然后再发送语音信息。初始同步信息由初始同步频率进行发送,根据发送的初始同步信息,初始同步频率分成两组,每组有4个同步频率组成,为了提高同步的抗干扰性能,同步的频率是随着时间的变化而更新的。第一组频率为f1、f2、f3、f4,每隔100个通信周期换掉一个同步频率,用于传送A组初始同步信息,传送完A组同步信息后插入两跳伪随机跳频(f9,f10)。第二组频率为f5、f6、f7、f8,也是每隔100个通信周期换掉一个同步频率,用于传送B组初始同步信息,传送完B组同步信息后插入两跳伪随机跳频(f11,f12)。每次按下PTT键,发送32跳的初始同步信息,其发送格式如图5所示。

图5 初始同步信息发送

正常跳频通信时在语音跳中间加传勤务同步跳,每800跳为一个通信循环,每80跳为一通信周期,每个通信周期传4跳(f1,f2,f3,f4)勤务同步信息发送。

结语

基于FPGA的跳频通信接收系统与常规跳频通信接收系统相比,该系统具有灵活性强、可靠性高、开发周期短和费用低等优点,可广泛应用于通信领域。在测试过程中发现本文设计的系统满足性能要求:4.8 kbps以下业务跳频同步时间小于6 s,4.8 kbps以上业务跳频同步时间小于0.6 s。