跳频技术是一种具有高抗干扰性、高抗截获能力的扩频技术[1]。接收系统是跳频通信系统中非常重要的部分,自适应跳频技术、高速跳频技术、信道编码技术、高效调制解调技术成为近年来跳频技术发展的新动态,基于FPGA的跳频通信接收系统[2]研究有很高的应用价值。

跳频电台就是采用了频率跳变来扩展频谱,提高抗干扰能力,在军事通信中得到了广泛的应用[3]。基于FPGA+DSP的跳频电台传输系统的设计方案[4]具有很好的可移植性。无线通信调制解调纷繁复杂,数码率及误码率要求也不尽相同,该传输系统还需要能够自适应地检测跳频电台的时钟信息及同步码,并进行相应的处理,以满足业务速率的接收解调。

本文系统中采用Xilinx公司的VIRTEX5 XC5VSX50T668 FPGA,该芯片具有先进的高性能逻辑架构,包含多种硬IP系统级模块,并且还支持以太网与PCI Exprees端点模块。其中RocketIO GTP收发器的设计运行速度为100 Mb/s~3.75 Gb/s,RocketIO GTX收发器的设计运行速度为150 Mb/s~6.5 Gb/s。

1 系统总体架构

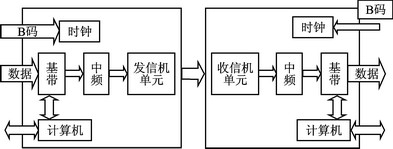

该系统采取半双工形式进行工作,通过 PTT进行收/发切换。高速跳频通信系统可具体化为发送状态模型和接收状态模型。本系统的硬件设备分为两个实体,一个负责发送数据,一个负责接收数据,主要的软件工作在基带板和中频板卡上。系统总体框架图如图1所示。

图1 系统总体框架图

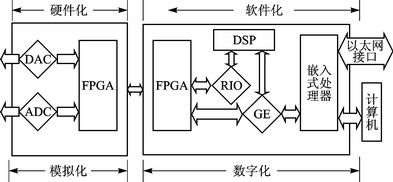

基带板芯片主要包括FPGA和DSP,处理器间使用RapidIO接口交换数据,中频板主要由FPGA和AD/DA转换芯片组成,基带板和中频板通过高速SERDES传输信号数据,基带信号经过信道编码、交织、软扩频,然后添加同步头,组成特定的帧格式后,写入FPGA 的发送消息存储区,其结构图如图2所示。

图2 基带板与中频板框图

从图2可以看出,在发送端,数据终端或语音终端将数字信息送入基带信号处理器(高速通用FPGA+DSP),然后DSP 对这些数字信息进行基带处理,得到数字化的基带信号并送入FPGA 进行数字中频处理(频谱上搬移过程),用数字化的方法将信号搬移中频上,数字化的中频信号再经过宽带D/A转换器转化为模拟信号,最后经由射频电路将载有信息的电磁波送入自由空间。