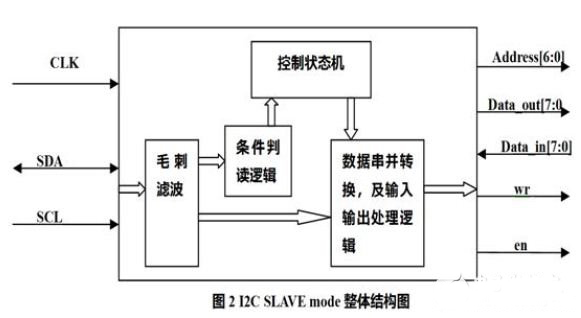

而且FPGA内部逻辑一般都工作在100MHz 以上,所以I2C 模块的系统时钟可以直接使用FPGA 的系统时钟,可以省去时钟转化模块,简化处理。当I2C 总线读FPGA 时,总线主器件在发送完第一个字节,FPGA 回复ACK 后,紧接着就要FPGA 输出相应的数据,所以在FPGA 逻辑发出ACK 的同时就要开始,FPGA 的内部寻址和读取相应的数据,在SCL 时钟频率最大值为400KHz 时,FPGA 的系统时钟为100MHz,那么FPGA 的内部逻辑有约250个时钟周期的寻址时间,这个时间是完全够用的。I2C SLAVEmode 整体结构图如图2.

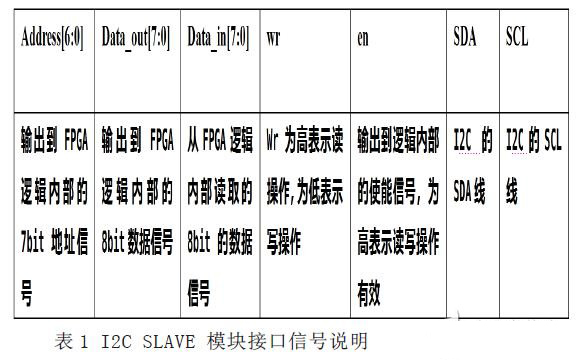

接口信号的说明如表1.

2 I2C SLAVE 模式控制器的设计与实现

2.1 I2C SLAVE 控制器的接口实现

I2C SLAVE 控制器的接口部分主要包括,信号异步时钟域的转换。输入滤波器,用来抑制毛刺。及SDA 线的双向转换。由于SDA 的PIN 是双向的,所以一定要分配在FPGA 的IO BLOCK块中,只有IO BLOCK 中有双向的硬件结构。因为SDA 和SCL信号的相位相对于FPGA 逻辑的系统时钟的相位关系是不确定的。