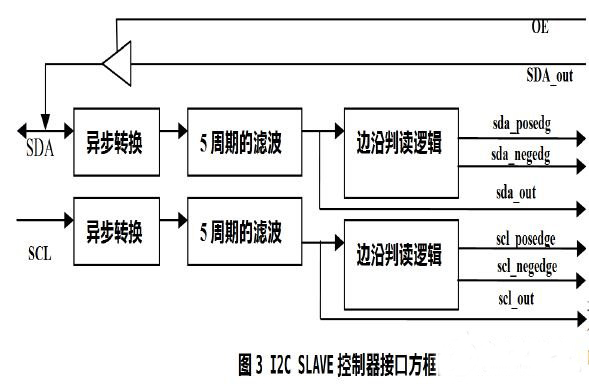

所以一定要进行异步时钟域的转换,以防止输入的寄存器出现亚稳态,它会使逻辑处在某个不确定的状态。此外FPGA的系统时钟频率比较高,对输入的毛刺比较敏感,故输入端要加入滤波器。接口部分的框图如图3.

异步时钟域的转换,采用两级寄存器的结构。输入滤波器采用5 级寄存器的结构。当采样到连续5 个高电平时,输出才为高电平,否则为低电平。接口部分的寄存器全都用FPGA 的系统时钟驱动。

2.2 I2C SLAVE 控制逻辑的实现

I2C SLAVE 控制逻辑状态机是整个模块的核心,所有I2C 总线相应的控制都由其完成。状态机有四个状态:IDLE,START,SAMPLE 和STOP 组成。Verilog 的定义如下:

`define IDLE 2‘b00

`define START 2’b01

`define STOP 2‘b10

`define SAMPLE 2’b11

下面介绍各个状态的功能。当I2C 总线无任何操作时控制器在IDLE 状态下,并保持。当接口逻辑判断到START 条件时,控制器跳转到START 状态下,并做好接受第一个字节的准备,包括初始化bit计数器。接着开始接受第一个字节包含7bit的地址和1bit 的读写状态位。当采集完第一个字节后,控制器跳到SAMPLE 状态下,开始执行数据字节的接受或发送。是接受或发送的状态由前一字节的最后1bit 的读写状态位决定。