当读写状态位为高时,表示I2C 总线的读操作,FPGA 逻辑发送数据。读写状态位为低时,表示I2C 总线的写读操作,FPGA逻辑接受数据。接着FPGA 逻辑发出一个ACK 信号后,表示可以进行读写操作。那么就进入到SAMPLE 状态下,正常读或写一个字节(也可以连续的读写多个字节,对此没有限制)。在完成8bit 数据读写后,I2C 的主器件会发出一个STOP 条件操作。fpga 逻辑收到后,就跳转到STOP 状态,并在几个时钟周期后,自动跳转到IDLE 状态下。从而完成一个完整的I2C 总线的读或写操作。

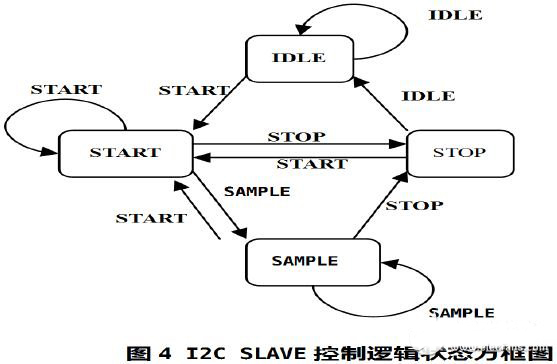

当然也包括一些异常处理,以防止状态机处在一个不确定的状态下。在SAMPLE 状态下如果遇到意外的START 条件时,即上次的总线操作没有完成就开始了下次的操作,则控制状态机会跳转到START 状态下,而开始接受这次新的总线操作,而上次的操作为无效。由如在SAMPLE 状态下,但是又收到一个START 条件。还有如在STOP 状态收到一个START 条件,处理也和上面一样。下图4 介绍了I2C SLAVE 控制逻辑状态机的状态跳转图。

如上图所示,在 SAMPLE 状态下,可以连续的读写数据,而地址是在读写完一个字节后由FPGA 逻辑自动加1 的。这样做使得I2C 总线的一次操作就可以连续对多个字节读或写。提高的总线的使用效率。

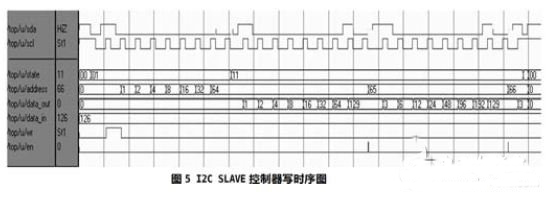

以下是在modelsim6.0 下进行的行为级仿真的时序图。

由自行编制的I2C 总线主器件BFM 驱动进行测试。图5 I2CSLAVE 控制器写时序图。

3 结论

本方案通过介绍SLAVE 模式的特点,给出设计的原理框图和modelsim 下的行为仿真时序图。在Altera 的Cyclone II 系列中用Quartus II 12.0生成的模块时钟频率可达到180MHz,占用的资源Totalcombinational functions 为83 个,Total registers 为41 个。而在实际应用中达100MHz 左右。证实了本方案操作简便,效果不错。