2.1 器件选型

该系统设计选用TI公司的TMS320VC5509A型DSP。该款DSP功耗低,片上资源丰富,主频最高可达200 MHz,片上带有128 K×16 bit RAM和32 K×16 bit ROM,内置6个DMA通道,1个I2C接口,3个McBSP接口,1个RTC模块,其外部存储器接口(EMIF)能与SDRAM无缝连接,同时还带有USB接口。FPAG选用ALTERA的Cyclone-II系列处理器,具有强大的逻辑处理能力,从而实现微处理器通用接口设计和简单信息预处理功能。

2.2 DSP与FPGA的接口设计

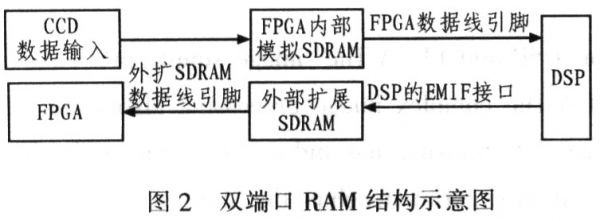

为保证系统实时性,DSP与FPGA之间的接口需实现大数据流通讯流畅的功能。将FPGA内部结果缓冲器模拟为SDRAM接口,一端输入CCD图像信号,一端输出图像数据并连接至DSP数据线。DSP的EMIF接口外接一片4 M×16 bit的SDRAM MT48LC4M16A2-75,通过将处理后的图像数据回传至外扩SDRAM,由FPGA实时读取并通过VGA接口显示,从而实现DSP与FPGA之间数据通讯功能。这两者之间配置的双端口RAM连接如图2所示。

DSP子系统主要包括电源管理单元、EMIF接口、SD卡接口、USB接口、JTAG调试接口和引导装载(Bootload)电路等。电源管理单元主要为系统提供稳定电源;EMIF接口主要用于外部扩展存储器;SD卡接口用于掉电后图像数据的存储;USB接口用于外接其他外设;JTAG接口用于电路调试等。

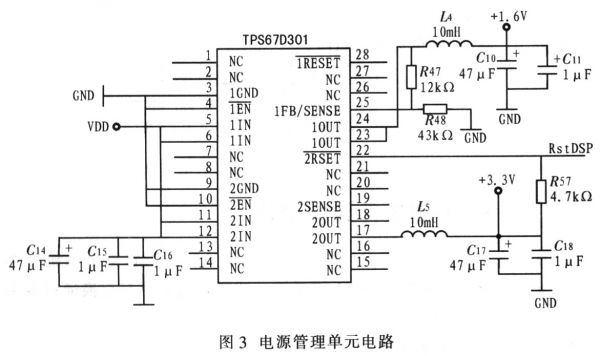

2.3.1 电源管理单元

DSP子系统供电可分为1.6 V和3.3 V两种,DSP内核需1.6 V供电,外设及I/O端口采用3.3 V供电,并需保证内核先于I/O上电,I/O先于内核掉电。该系统采用电源器件TPS767D301配置不同电压值。该器件包括两路电压输出,每路最大输出电流可达1 A.输出电压稳定。图3为电源管理单元电路。