3.4 FPGA子系统组成及功能

为实现该图像处理平台通用性和实时性,FPGA子系统需实现的功能包括:开放式的图像数据采集总线,DSP图像处理实时数据总线,100 MB以太网接口,UART接口,VGA实时显示模块,I2C存储器接口和PS/2接口等。其中UART接口方便系统软件开发及调试,VGA接口用于图像数据实时显示,I2C接口外接EEPROM用于系统参数的掉电存储。为实现多个系统的网络化,FPGA子系统还设有以太网接口,用于多个系统将处理结果回传至PC端口。PS/2接口为预留端口,后期根据需要增加键盘等输入设备。

4 系统软件设计

4.1 软件开发开具

该系统软件设计采用TI公司CCS3.1(Code ComposerStudio)作为开发环境,并利用CCS自带的DSP/BIOS实时操作系统进行设计。在CCS中完成软件的编辑、编译、调试、代码性能测试和项目管理等工作。通过使用DSP/BIOS提供的一系列丰富的内核服务,快速创建满足实时性能要求的精细复杂的多任务应用程序。DSP/BIOS内核具有跨平台的标准API接口,能被用户程序调用,易于移植。此外,这些服务除支持多线程调度管理外,还支持系统实时分析以及资料管理。DSP/BIOS内核具有很大的尺寸伸缩性,多线程配置下的内核镜像的代码量最小仅有1 K字,占用DSP资源非常少。

4.2 软件系统总体设计

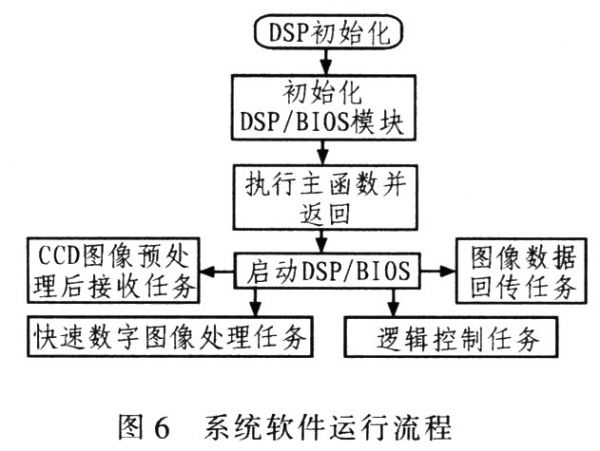

在硬件平台基础上,利用CCS集成开发环境中的DSP/BIOS实时操作系统内核,开发具有可扩展性的软件系统。系统软件部分采用模块化和层次化设计思想。软件结构主要包括:设备驱动层、操作系统层、应用程序接口(API)层和应用层。设备驱动层负责与硬件有关的各个模块或外设的驱动程序设计;操作系统层负责嵌人式实时操作系统移植;应用程序接口层完成系统控制功能、数据读写等,并实现硬件无关性;应用层则设计与系统应用背景有关的控制程序。图6为系统软件运行流程。软件设计主要分为CCD图像预处理后的接收任务、快速数字图像处理任务、逻辑控制任务和图像数据回传任务。系统上电后,程序首先执行DSP的初始化和DSP/BIOS初始化,接着执行函数主体并启动DSP/BIOS操作系统,以后的任务均由操作系统进行调度。采用嵌入式实时操作系统DSP/BIOS构建的图像处理软件平台能较好满足任务对实时性的要求,且结构稳定紧凑,可移植性高。