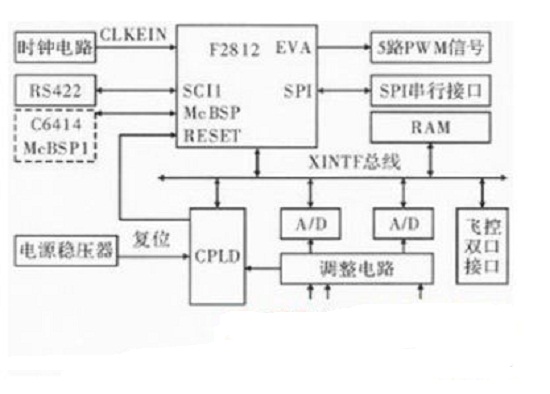

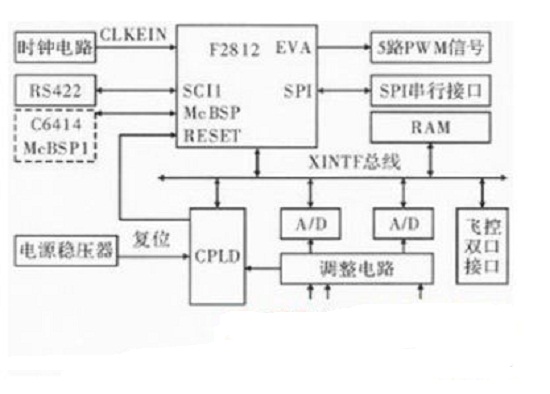

3 控制信息处理模块的硬件设计

控制信息处理板由处理器、时钟及复位电路、存储器、数字脉冲计数与逻辑控制电路、模数转换A/D电路和指示灯电路组成。如图3所示。

控制信息处理板信号处理器采用TMS320F2812,由30 MHz晶体提供输入工作时钟,16位总线宽度,可访问128 kW的片上程序存储空间和64

kW的数据存储空间,具有三级外部中断。时钟电路采用外部晶振为F2812提供30 MHz的时钟输入,由内部PLL电路配置F2812工作时钟为120

MHz,外部总线工作时钟为60

MHz。复位电路由本板的LDO电源转换器输出,复位输入经CPLD的逻辑控制均产生控制信息处理板DSP的复位。控制信息处理板主要有以下存储器配置:F2812片内存储器包括:18

kW的SARAM、128 kB的Flash、4 kB的Boot Rom。片外存储空间包括:512kB的SRAM、1

kB的飞控计算机双口存储空间、3路数字脉冲计数电路的数据寄存器及板上2片A/D转换器的数据端口地址等。

可编程逻辑CPLD电路完成控制信息处理板的3路数字脉冲计数、复位电路和译码逻辑等,译码逻辑由F2812的外部存储器片选信号和高位地址线一并通过逻辑译码产生访问A/D芯片及与飞控模块接口的片选信号。

CPLD实现对3路数字脉冲信号进行计数测频的原理是;将3路数字脉冲信号经CPLD测频电路对脉冲信号进行计数处理后,通过软件编程由F2812定时读取。

2片A/D转换器实现9路模拟量输入的模数转换,A/D电路见图4。系统输入9路差分交流模拟信号,这9路模拟信号需使用差分运放调整至0~+5

V,同时输入到A/D转换器,采样时钟由CPLD控制。